- 您现在的位置:买卖IC网 > Sheet目录344 > MPC8569E-MDS-PB (Freescale Semiconductor)BOARD MOD DEV SYSTEM MPC8569

�� �

�

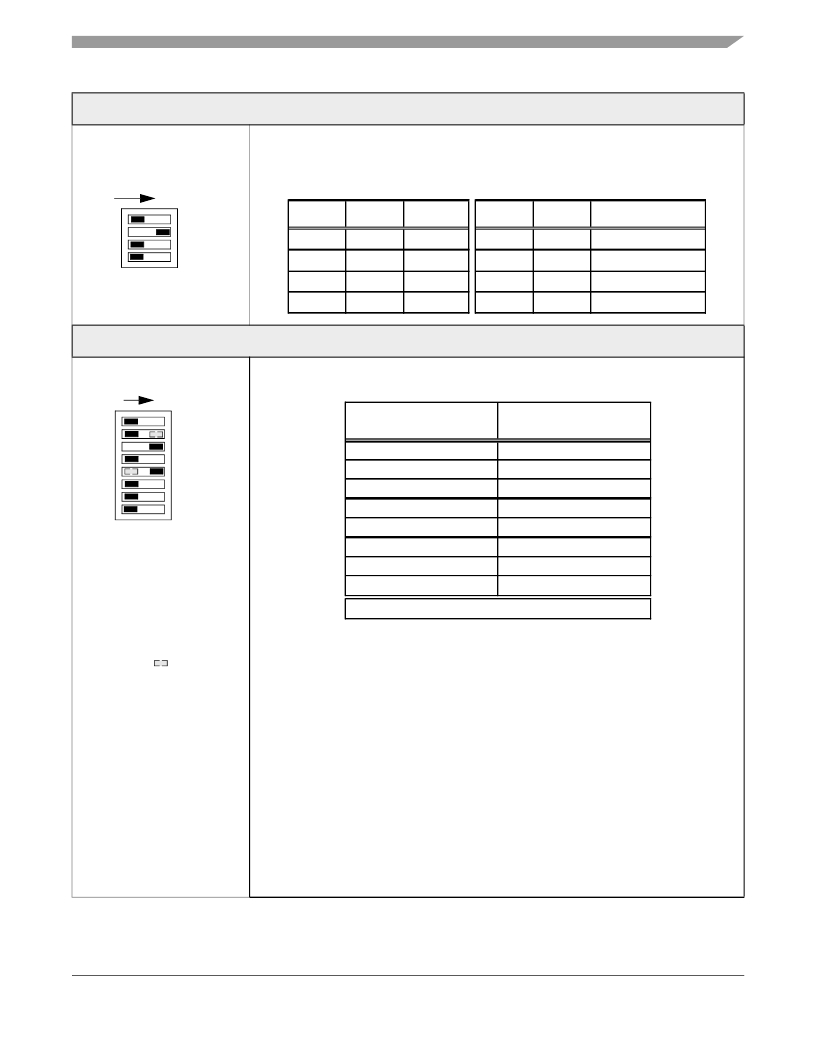

Switch� Default� Settings�

�SW1� Configuration:� SerDes� CLK�

�SW1.1-SW1.4:� SerDes� Reference� Clock�

�?� Sets� reference� clock� value� for� MPC8569� SerDes� module.�

�?� Sets� reference� clock� values� for� external� PEX/SRIO/SGMII� interfaces.�

�?� (Default)� 100� MHZ� and� no� spread.�

�ON� ’0’�

�1�

�2�

�3�

�4�

�FSEL0�

�FSEL1�

�SSC0�

�SSC1�

�FSEL0�

�0� (ON)�

�1� (OFF)�

�FSEL1�

�0� (ON)�

�0� (ON)�

�Q0:Q1�

�25� MHz�

�100� MHz�

�SSC0�

�0� (ON)�

�1� (OFF)�

�SSC1�

�0� (ON)�

�0� (ON)�

�SPREAD%�

�CENTER� +/-� 0.25�

�DOWN� -0.5�

�0� (ON)�

�1� (OFF)� 125� MHz�

�0� (ON)� 1� (OFF)�

�DOWN� -0.75�

�1 (OFF) 1 (OFF) 25 OMHz�

�1� (OFF)� 1� (OFF)�

�NO� SPREAD�

�SW5� Configuration:� DDR3�

�SW5.1-� SW5.3:� DDR� Complex� Clock� PLL� Ratio�

�?� Establish� clock� ratio� between� SYSCLK� input� and� DDR� complex� clock.�

�ON� ’0’�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�NOTE!�

�CLK_PLL0�

�CLK_PLL1�

�CLK_PLL2�

�FB� SEL�

�TYPE�

�MODE�

�SPEED�

�FIX�

�Value� (Binary)�

�000�

�001�

�010�

�011�

�100�

�101�

�110�

�111�

�DDR� Complex� Clock:�

�SYSCLK� Ratio�

�3:1�

�4:1�

�5:1�

�6:1�

�8:1�

�10:1�

�(Default)� 12:1�

�Synchronous� Mode*�

�Switch� positions� related�

�to� DDR2� usage� are�

�marked� with� the� symbol:�

�Freescale� Semiconductor�

�*Synchronous� mode:� DDR� data� rate� =� CCB� clock.�

�SW5.4:� DDR� PLL� Feedback� Select�

�?� ‘0’:� Local/Shorter� feedback� path� selected�

�?� ’1’:� (Default)� Longer� feedback� path� selected� (matches� insertion� delay� of� DDR,QE� and�

�Platform�

�SW5.5:� DDR� SDRAM� Type�

�?� ‘0’:� (Default)� DDR3,� 1.5V,� CKE� low� at� reset.�

�?� ’1’:� DDR2,� 1.8V,� CKE� low� at� reset.�

�SW5.6:� DRAM� Mode�

�?� ‘0’:� Primary� and� secondary� DDR� is� enabled� (32-bit� width� data� bus).�

�?� ‘1’:� (Default)� Primary� DDR� is� enabled� (64-bit� width� data� bus);� secondary� DDR� is� disabled.�

�SW5.7:� DDR� Speed�

�?� ‘1’:� (Default)� DDR� clock� frequency� <� 500MHz.�

�?� ‘0’:� DDR� clock� frequency� >� or� =� to� 500MHz.�

�SW5.8:� Disables� DDR2� Phase� Reset� Logic�

�?� ‘0’:� DDR� controller� disables� MCKE� at� reset;� a� few� cycles� later� MCK� is� disabled.�

�?� ’1’:� (Default)� At� reset,� DDR� controller� simultaneously� disables� MCK� and� MCKE.�

�MPC8569E-MDS-PB� Hardware� Getting� Started,� Rev.� 3.1�

�9�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MPC8572EAMC

MPC8572 AMC RAPID SYSTEM

MPQ-ARM

ISP 4PORT FOR ARM CORTEX MCU

MP

SURGE SUPPRESSR 2/RJ11 MODEM/FAX

MR0A08BCYS35

IC MRAM 1MBIT 35NS 44TSOP

MR0D08BMA45R

IC MRAM 1MBIT 45NS 48BGA

MR256A08BCYS35R

IC MRAM 256KB 35NS 44TSOP

MR256D08BMA45R

IC MRAM 256KB 45NS 48BGA

MR25H10CDF

IC MRAM 1MBIT 40MHZ 8DFN

相关代理商/技术参数

MPC8569EVTANKGB

功能描述:数字信号处理器和控制器 - DSP, DSC 8569 800MHz rev2.1

RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

MPC8569EVTAQLJB

功能描述:数字信号处理器和控制器 - DSP, DSC 8569 1GHz rev2.1

RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

MPC8569EVTAUNLB

功能描述:数字信号处理器和控制器 - DSP, DSC 8569 1.33GHz rev2.1

RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

MPC8569VJAUNLB

制造商:Freescale Semiconductor 功能描述:IC MPU PWRQUICC 1333MHZ 783FCBGA

MPC8569VTANKGB

功能描述:数字信号处理器和控制器 - DSP, DSC 8569 ST 800/600/400 r2.1 RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

MPC8569VTAQLJB

功能描述:数字信号处理器和控制器 - DSP, DSC 8569 ST 1067/667/533 r2.1 RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

MPC8569VTAUNLB

功能描述:数字信号处理器和控制器 - DSP, DSC 8569 ST 1333/667/533 r2.1 RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

MPC8572CLVTAULD

功能描述:微处理器 - MPU 1333 LOW PWR EXT TEMP RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324